# Design of RAM using Pulsed Latch Based Shift Register

# P. Mounika<sup>1</sup> | P. Soundarya mala<sup>2</sup>

<sup>1</sup>PG Scholar, Department of ECE, Godavari Institute of Engineering and Technology, Rajahmundry, Andhra Pradesh, India.

<sup>2</sup>Associate Professor, Department of ECE, Godavari Institute of Engineering and Technology, Rajahmundry, Andhra Pradesh, India.

# ABSTRACT

In this paper proposed for low power area efficient for shift register based SRAM design using pulsed latches. The area, delay and power consumption reduced by flip-flop design replace with pulsed latches. In this method reduce the timing problem. In this paper proposed for 256 bit shift register SRAM. Verilog HDL has been used to implement the various blocks and simulation done using Xilinx simulator. RTL implementation has been done using Xilinx ISE suite 14.3.

KEYWORDS: RAM, Shift register, Pulsed latch, Low Power Design

Copyright © 2016 International Journal for Modern Trends in Science and Technology All rights reserved.

# I. INTRODUCTION

Flip flops are the basic storage elements used appreciably in all sorts of digital designs. because the characteristic size of CMOS era method scaled down in keeping with Moore's law, designers are able to combine many numbers of transistors onto the equal die. The extra transistors there might be extra switching and more strength dissipated inside the shape of warmth or radiation. warmness is one of the phenomenon packaging challenges on this epoch, it's miles one of the fundamental challenges flow strength design methodologies and practices. another motive force of low strength research is the reliability of the integrated circuit. extra switching implies higher common modern is expelled and consequently the opportunity of reliability problems happening rises. we are shifting from laptops to drugs and even smaller computing digital structures. With this profound fashion persevering with and without a match trending in battery lifestyles expectancy, the greater low strength issues will ought to bead dressed. The contemporary traits will finally mandate low

strength design automation on a very huge scale to match the tendencies of power consumption of today's and future integrated chips[3]. electricity intake of Very large Scale incorporated design is given by generalized relation, P = CV2f [1]. for the reason that strength is proportional to the square of the voltage as per the relation, voltage scaling is the most distinguished manner to reduce energy dissipation. but, voltage scaling is results in threshold voltage scaling which bows to the exponential growth in leakage energy. even though numerous contributions were made to the art of single side induced flip-flops, a want obviously happens for a layout that in addition improves the overall performance of unmarried facet triggered flip flops[2].patterns.

The structure of a shift register is quite easy. An N-bit shift sign in consists of collection connected N data flip-flops. The rate of the flip flop is less crucial than the area and power consumption due to the fact there may be no circuit between flip-flips in the shift sign in. The smallest turn-flop is appropriate for the shift register to lessen the place and electricity consumption. lately, pulsed latches have replaced flip-flops in lots of applications, due to the fact a pulsed latch is tons smaller than a flip flop [6]–[9].but the pulsed latch can not be utilized in a shift sign in due to the timing problem between pulsed latches.

# II. PROPOSED PULSE LATCHES

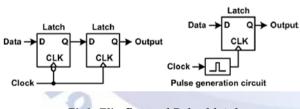

A master-slave flip-flop the use of latches in Fig. 1 may be replaced by using a pulsed latch which includes a latch and a pulsed clock signal fig four. For the pulsed clock sign all the pulsed latches proportion the heart beat technology circuit. Due to this sharing of the pulse clock circuit the area and power consumption intake of the circuits reduces to almost half of the master slave flip flop.

- It has a downside that the pulsed clock generator can't be used directly on this circuit because of its timing troubles.

- To overcome this numerous steps may be applied consisting of to add delay circuits between latches use multiple non-overlap delayed pulsed clock signals

All though both the above noted techniques resolve the timing hassle the postpone circuits gift project within the place and power intake area ,so it's far excellent within the hobby of low strength and region designing to utilize the non over lapping more than one not on time pulse clock indicators

Fig1: Flip-flop and Pulsed latch

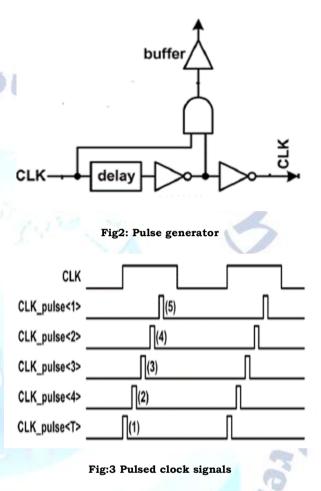

# **Pulse Generator:**

Every pulsed clock sign arrives at the sub shift registers at different time because of the heartbeat skew within the wire. the heartbeat skew increases proportional to the wire distance from the delayed pulsed clock generator. All pulsed clock alerts have nearly the equal pulse skews while they arrive at the equal sub shift check in. consequently, inside the same sub shift sign in, the heart beat skew differences among the pulsed clock indicators are very small. The clock pulse durations larger than the pulse skew differences cancel out the outcomes of the heart beat skew differences. every other solution is to insert clock buffers and clock bushes to send the short clock pulse with a small wire postpone. How ever this increases the region and strength overhead. Further more, the more than one clock pulses make the more overhead for more than one clock buffers and clock timer.

# III. PROPOSED RAM DESIGN

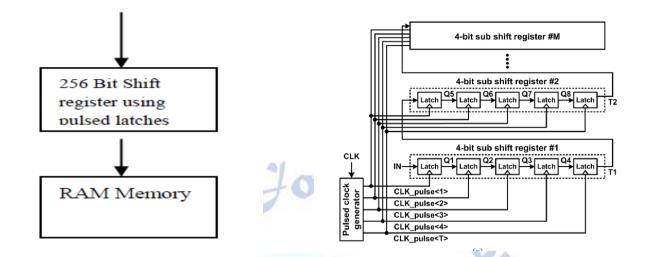

On this paper proposed for Shift check in using SRAM design with help of pulsed clock generators. The memory save the 256 bit facts's. static Random-get right of entry to reminiscence (RAM) can be a fashion of semiconductor memory that uses bi-solid latching electronic system to save every bit. The time period static differentiates it from dynamic RAM (DRAM) that must be sporadically invigorated. SRAM reveals understanding remembrance; but it is nevertheless unstable within the typical feel that information is eventually misplaced once the reminiscence is not steam-powered. For increasing the battery standby time I'm developing with a replacement fashion of RAM cell that consumes less power than the triumphing SRAMs. the key objective in the back of this paper is to cut back the facility consumption of random access memory.

#### Fig4: RAM memory using shift register

# Write operation:

For writing 1/0 we should provide the data to the bit line (BL), with respect to the bit line bar ( $BL\overline{D}$ ). When the word line (WL) is enabled the data is written into respective node.

# **Read Operation:**

When the word line (WL) is enabled, the bit line which connected to the node of the cell containing '0' is discharged. Using sense amplifiers we can know the node containing 1/0 by sensing the bit lines. The bit line containing '1' means it's connected to the node containing '1' and vice versa.

## **Design Implementation:**

While designing any circuit or chip it's vital to bear in mind different factors answerable for it to be implemented in actual existence. The most clock frequency in the conventional shift sign up is constrained to most effective the postpone of turn-flops due to the fact there is no delay between flip-flops. therefore, the vicinity and electricity consumption are more critical than the velocity for choosing the turnflop. The proposed 256-bit shift register uses 4 latches and it plays shift operation with five non overlap not on time pulse clock signals (CLK\_pulse). 256 latches store 256 bit statistics (Q1-Q256). The series of the pulsed clock signals is in the opposite sign of the four latches. The shift register outputs stored to SRAM circuits .finally the Shift register design get less area and less power consumption with help of pulsed clock generators.

IV. RESULTS

Fig5: Shift register

#### **Table 1: Power Analysis**

| Target devices | Kintex-xc7k70t |

|----------------|----------------|

| Leakage Power  | 0.080Watts     |

In this paper, we have proposed a novel deployment of all optical implementation of sequential circuits based on MZI functionality using reversible logic. The design of all optical implementation reversible counters is new one. Our design can be extended up to n-bit counter

also. By using this reversible logic functionality finite state machines can also be designed. Reversible logic has enormous advantages over conventional logic.

#### V. CONCLUSION

The timing problem between pulsed latches is solved using more than one non-overlap not on time pulsed clock indicators rather than a single pulsed clock sign. A small range of the pulsed clock indicators is utilized by grouping the latches to numerous sub shifter registers and the usage of extra transient garage latches. The implementation results of proposed and traditional architectures based totally on Xilinx FPGA Spartan XC3S200 are summarized.

#### REFERENCES

- [1] Low-Power and Area-Efficient Shift Register Using Pulsed Latches Byung-Do Yang.

- [2] M. Hatamian *et al.*, "Design considerations for gigabit ethernet 1000 base-T twisted pair transceivers," *Proc. IEEE Custom Integr. Circuits Conf.*, pp

- [3] H. Yamasaki and T. Shibata, "A real-time image-feature-extraction and myector-generation vlsi employing arrayed-shift-register architecture," *IEEE J. Solid-State Circuits*, vol. 42, no. 9, pp. 2046–2053, Sep. 2007.

- [4] H.-S. Kim, J.-H. Yang, S.-H. Park, S.-T. Ryu, and G.-H. Cho, "A 10-bit column-driver IC with parasitic-insensitive iterative charge-sharing based capacitor-string interpolation for mobile active-matrix LCDs," *IEEE J. Solid-State Circuits*, vol. 49, no. 3, pp. 766–782, Mar. 2014.

- [5] S.-H. W. Chiang and S. Kleinfelder, "Scaling and design of a 16-megapixel CMOS image sensor for electron microscopy," in *Proc. IEEE Nucl. Sci. Symp. Conf. Record (NSS/MIC)*, 2009, pp. 1249– 1256.

- [6] S. Heo, R. Krashinsky, and K. Asanovic, "Activity-sensitive flip-flop and latch selection for reduced energy," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 15, no. 9, pp. 1060– 1064, Sep. 2007.

- [7] S. Naffziger and G. Hammond, "The implementation of the nextgeneration 64 b itanium microprocessor," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2002, pp. 276–504.

- [8] H. Partovi et al., "Flow-through latch and edgetriggered flip-flop hybrid elements," IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, pp. 138–139, Feb. 1996. E. Consoli, M. Alioto, G. Palumbo, and J. Rabaey, "Conditional push-pull pulsed latch with 726 fJops energy delay product in 65 nm CMOS," in IEEE Int.

Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2012, pp. 482–483.

[9] V. Stojanovic and V. Oklobdzija, "Comparative analysis of masterslave mlatches and flip-flops for high-performance and low-power systems," *IEEE J. Solid-State Circuits*, vol. 34, no. 4, pp. 536–548, Apr. 1999.